1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

|

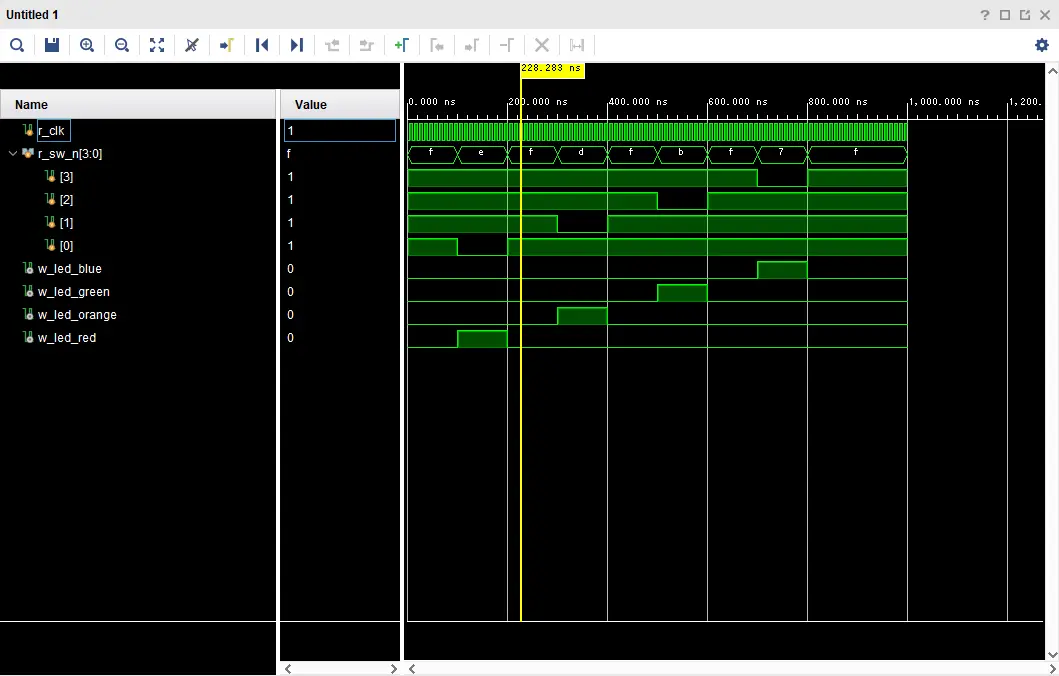

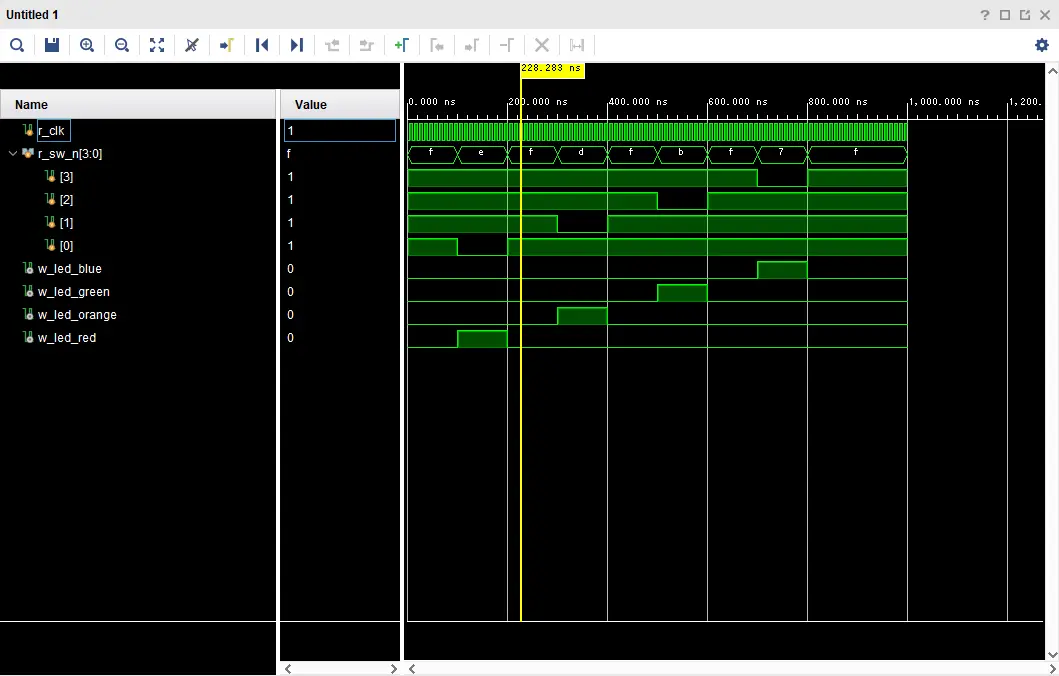

`timescale 1ns / 100ps

module top_tb;

// 信号を定義

reg r_clk;

reg [3:0] r_sw_n;

wire w_led_blue;

wire w_led_green;

wire w_led_orange;

wire w_led_red;

// 100MHzクロック信号を生成

initial begin

r_clk = 0;

end

always #(5) begin

r_clk <= ~r_clk;

end

// スイッチ信号を生成

initial begin

#0 r_sw_n[3:0] = 4'b1111;

#100 r_sw_n[3:0] = 4'b1110;

#100 r_sw_n[3:0] = 4'b1111;

#100 r_sw_n[3:0] = 4'b1101;

#100 r_sw_n[3:0] = 4'b1111;

#100 r_sw_n[3:0] = 4'b1011;

#100 r_sw_n[3:0] = 4'b1111;

#100 r_sw_n[3:0] = 4'b0111;

#100 r_sw_n[3:0] = 4'b1111;

end

// top.vを読み出す

top top_inst (

.i_clk (r_clk)

,.i_sw_n (r_sw_n)

,.o_led_blue (w_led_blue)

,.o_led_green (w_led_green)

,.o_led_orange (w_led_orange)

,.o_led_red (w_led_red)

);

endmodule

|